Prodigy's I3C Analyzer Fortifies AI and HPC Infrastructure

- $39 billion: Global market value for test and measurement equipment in 2024, projected to exceed $47 billion by 2029. - 12.5 MHz: Maximum data rate offered by the MIPI I3C interface, significantly higher than predecessors. - 4 key protocols: NVMe-MI, SPDM, PLDM, and MCTP supported by Prodigy's I3C Analyzer for comprehensive validation.

Experts agree that Prodigy's enhanced I3C Analyzer addresses critical validation needs for AI and HPC infrastructure, offering a unified solution for testing complex communication stacks and improving system reliability.

Prodigy's I3C Analyzer Fortifies AI and HPC Infrastructure

BENGALURU, India – March 25, 2026 – As the demands of artificial intelligence, high-performance computing (HPC), and next-generation data centers push hardware to its limits, the intricate communication pathways within these systems have become a critical focus for innovation and validation. Prodigy Technovations, a key player in protocol analysis solutions, has announced a significant enhancement to its PGY-I3C-EX-PD I3C Protocol Exerciser and Analyzer, aiming to address the complex validation needs of this new era.

The update introduces comprehensive support for crucial application-level management protocols, including NVMe-MI, SPDM, and PLDM, which operate over the I3C interface. This move enables engineers to test and validate not just the foundational data transport but also the sophisticated management, security, and communication functions that are essential for the stability and performance of modern computing platforms built on DDR5 memory and CXL interconnects.

The Growing Complexity of Platform Management

For decades, simple interfaces like I2C and SMBus were sufficient for basic system management tasks. However, the relentless pace of technological advancement has rendered them bottlenecks. Modern systems, from sprawling AI data centers to compact, powerful edge devices, require a more robust and efficient communication backbone for sideband management. This is the role that the MIPI I3C interface is increasingly designed to fill.

Adopted by major standards bodies like JEDEC for DDR5 memory modules and PCI-SIG for CXL (Compute Express Link), I3C offers significantly higher data rates (up to 12.5 MHz), lower power consumption, and advanced features like in-band interrupts compared to its predecessors. It serves as a high-speed digital pipeline for critical management traffic.

However, the I3C interface is only the transport layer. The actual management intelligence—device discovery, security authentication, firmware updates, and telemetry monitoring—is handled by higher-level protocols that run on top of it. These include:

* MCTP (Management Component Transport Protocol): A transport protocol that enables system management software to communicate with various management-enabled components inside a platform.

* NVMe-MI (NVM Express Management Interface): Used for out-of-band management of NVMe solid-state drives (SSDs).

* SPDM (Security Protocol and Data Model): Provides authentication, firmware measurement, and security capabilities for hardware components.

* PLDM (Platform Level Data Model): Defines formats for monitoring, controlling, and updating platform hardware.

Validating these stacked protocols presents a formidable challenge for engineers. They must ensure that the entire communication chain, from the physical I3C layer up through the complex application logic, is free of errors and interoperability issues. A failure at any point can lead to system instability, security vulnerabilities, or performance degradation—risks that are unacceptable in mission-critical AI and HPC environments.

Bridging the Validation Gap for Next-Gen Systems

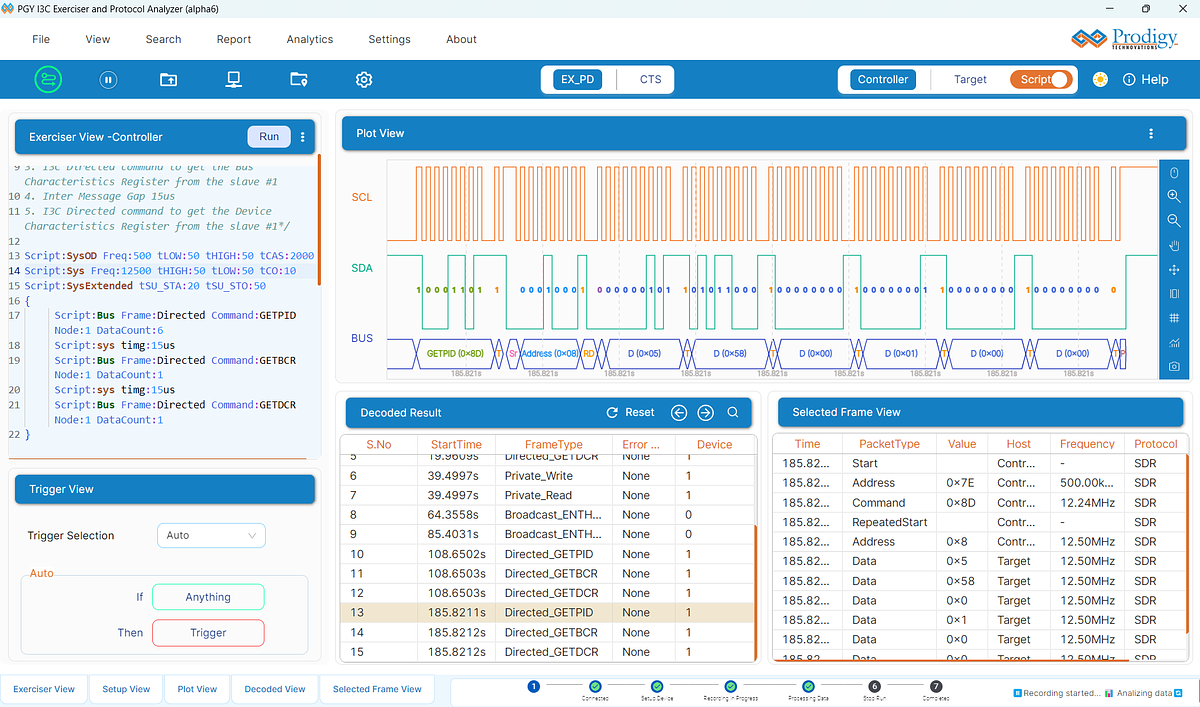

Prodigy Technovations' enhanced PGY-I3C-EX-PD is engineered to bridge this validation gap. By integrating support for these critical application-layer protocols, the tool provides a unified solution for testing the entire communication stack. Engineers can now generate and analyze traffic that simulates real-world management scenarios, from a simple temperature check on a DDR5 memory module to a secure firmware update on a CXL-attached accelerator.

"The growth of AI infrastructure and high-performance computing platforms is changing how devices communicate, manage system intelligence," said Godfree Coelho, Founder & CEO of Prodigy Technovations, in the company's announcement. "I3C is becoming an important interface for platform management across servers, storage, and memory subsystems. With these enhancements, engineers can validate both the I3C protocol and the management protocols built on top of it."

The solution functions as both a protocol analyzer, passively monitoring and decoding traffic, and an exerciser, actively generating traffic and emulating different device roles. It can operate as an I3C Controller, Target, or Secondary Controller, allowing developers to test their designs against a compliant and configurable counterpart. Key features like advanced error injection and margin testing enable engineers to push their designs to the limit, uncovering corner-case bugs that might otherwise only appear in production environments. This comprehensive testing capability is designed to accelerate development cycles and significantly improve the reliability of the final product.

Navigating a Competitive and Evolving Landscape

The market for test and measurement equipment is expanding in direct response to the growing complexity of electronic systems. The global market was valued at nearly $39 billion in 2024 and is projected to exceed $47 billion by 2029. Within this landscape, the niche for I3C validation is becoming increasingly competitive as I3C adoption accelerates.

While several companies offer tools for I3C protocol analysis, Prodigy Technovations' strategic focus on integrated support for the full suite of application-layer protocols—NVMe-MI, SPDM, and PLDM over MCTP—appears to be a significant differentiator. This holistic approach directly addresses the most pressing challenges faced by engineers working on the latest server and HPC architectures. The addition of a new, streamlined user interface further aims to simplify the complex task of debugging these multi-layered protocol interactions.

The tool's support for I3C versions up to 1.2 and its ability to emulate legacy I2C devices also make it valuable for validating hybrid environments, which are common during the industry's transition period. This ensures that new I3C-enabled components can coexist and communicate reliably with older parts of a system, a practical necessity in complex SoC and platform designs. As the industry continues its rapid march toward more disaggregated and interconnected systems powered by CXL and other advanced technologies, the need for such comprehensive validation tools is only expected to grow.

📝 This article is still being updated

Are you a relevant expert who could contribute your opinion or insights to this article? We'd love to hear from you. We will give you full credit for your contribution.

Contribute Your Expertise →