Beyond the Chip: How System-Level Design Is Reshaping AI's Future

- 3-5x higher interconnect density achieved by Alchip's 3DIC platform

- 30-40% less energy consumed per bit of data moved with the new system-level design

- Up to 35% lower latency in AI processing tasks

Experts agree that the future of AI hardware lies in system-level design, where modular chiplet architectures and advanced packaging technologies are essential for overcoming performance and efficiency bottlenecks.

Beyond the Chip: How System-Level Design Is Reshaping AI's Future

TAIPEI, TAIWAN – April 17, 2026 – As the artificial intelligence revolution accelerates, the very foundation of computing hardware is being rebuilt. The decades-long dominance of the monolithic chip is giving way to a new paradigm: intricate, system-level designs that stack and connect specialized "chiplets" like digital Lego blocks. In a significant move highlighting this industry-wide pivot, ASIC design leader Alchip Technologies has unveiled a 3DIC platform that promises to manage this complexity, enabling the creation of more powerful and efficient AI processors.

The announcement underscores a critical reality in the semiconductor world: simply shrinking transistors is no longer enough to satisfy the exponential growth in AI compute demand, which now doubles every few months. The future of AI performance lies in architecture and integration.

The End of the Monolithic Era

For years, the blueprint for a powerful processor was a single, massive piece of silicon—a monolithic die. But this approach is hitting fundamental physical and economic walls. As these chips grow to the size of a dinner plate, they bump against reticle limits (the maximum size that can be patterned in one go), suffer from lower manufacturing yields, and incur skyrocketing mask costs.

More critically, a growing share of a chip's energy budget is spent not on computation, but on moving data. This "memory wall" becomes a critical bottleneck for next-generation AI accelerators that require multi-terabyte-per-second memory bandwidth to feed their processing engines.

The industry's solution is heterogeneous integration, a strategy that breaks down a large System-on-Chip (SoC) into smaller, optimized chiplets. A compute-intensive function can be built on a cutting-edge 2-nanometer process, while an I/O controller can remain on a more mature, cost-effective node. These chiplets are then assembled within a single advanced package, allowing designers to mix and match the best technology for each job, improving yield, reducing costs, and accelerating development. This modular approach is no longer a niche strategy; it is a survival tactic adopted by nearly every major player, including AMD, Intel, and even NVIDIA in its latest designs.

A System in a Package: Alchip's 3.5D Approach

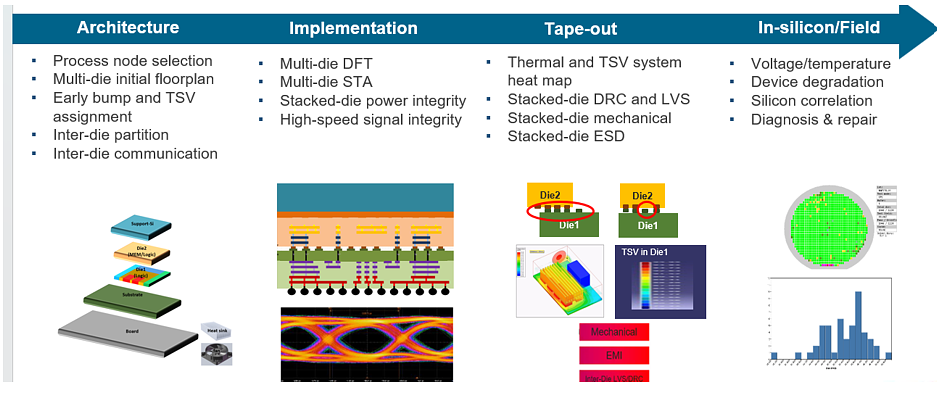

Alchip's new 3DIC platform formalizes this system-level approach into a comprehensive design and integration service. The company dubs its architecture a "3.5D" platform, a hybrid that combines the horizontal scaling of chiplets on an interposer (a technique known as 2.5D) with the selective vertical stacking of dies (true 3D integration).

This method allows for unprecedented design flexibility. A typical configuration might involve multiple high-performance compute chiplets sitting side-by-side, communicating with stacks of High Bandwidth Memory (HBM), all while being connected to I/O and other logic dies that can be stacked vertically to save space and shorten communication paths.

To achieve this, Alchip integrates a suite of the industry's most advanced packaging technologies, including TSMC's CoWoS family (Chip-on-Wafer-on-Substrate) and its pioneering SoIC-X direct-bonding technology. The result, according to the company, is a dramatic improvement in the metrics that matter most for AI: up to 3-5 times higher interconnect density, 30-40% less energy consumed per bit of data moved, and up to 35% lower latency. These gains are crucial for tackling the power and bandwidth conundrums that plague modern data centers, where AI systems can consume multiple kilowatts of power per package.

The Race for Advanced Packaging Dominance

Alchip's announcement places it at the center of a fiercely competitive landscape. The ability to package complex chiplet systems is now a key strategic asset, and the main battle is being fought between the world's foundry giants. TSMC, the world's largest contract chip manufacturer, is the undisputed leader with its CoWoS technology, which is essential for nearly all top-tier AI accelerators. The demand is so intense that TSMC is boosting its CoWoS capacity by over 60% in 2025, yet supply is expected to remain tight.

Meanwhile, competitors like Samsung Foundry with its I-Cube and X-Cube technologies, and Intel Foundry with its Foveros 3D stacking and EMIB solutions, are investing billions to capture a piece of the lucrative AI hardware market.

In this high-stakes environment, Alchip operates as a crucial design and integration partner. It provides the specialized expertise needed to navigate the complexities of multi-die systems for customers—from hyperscale cloud providers developing custom silicon to ambitious AI startups—that lack their own foundry relationships or deep packaging expertise. By offering a unified design flow that co-optimizes silicon, packaging, and thermals, Alchip allows its clients to focus on their unique AI workloads rather than the labyrinthine process of physical integration.

Building the New AI Infrastructure

The shift to system-level design is being enabled and accelerated by new industry standards. The Universal Chiplet Interconnect Express (UCIe) protocol, now in its third iteration, provides a common language for chiplets from different vendors to communicate, paving the way for an open, multi-vendor chiplet marketplace. This is a critical step in preventing vendor lock-in and fostering broader innovation.

For hyperscale cloud providers and HPC companies, the ability to commission custom ASICs using platforms like Alchip's is a game-changer. It allows them to create bespoke hardware perfectly tuned for their specific algorithms, whether for large language model training or complex scientific simulations, giving them a significant competitive advantage over those relying on off-the-shelf components.

"AI innovation no longer happens at the chip level alone. It’s fast moving to the system level," said Johnny Shen, Chairman, CEO and President of Alchip Technologies, in a statement. "Our 3DIC platform gives customers the flexibility to architect around their workloads while we manage the complexity of integration, packaging, and production."

As AI systems continue to grow in complexity and scale, the focus of innovation is irrevocably shifting from the transistor to the system. The companies that master the art of integrating disparate pieces of silicon into a cohesive, high-performance whole will be the ones who build the future of artificial intelligence.

📝 This article is still being updated

Are you a relevant expert who could contribute your opinion or insights to this article? We'd love to hear from you. We will give you full credit for your contribution.

Contribute Your Expertise →